ATmega128 리셋 벡터 / 인터럽트 벡터

ATmega128에서는 리셋 벡터를 포함하여서 총 35개의 인터럽트 벡터를 가지고 있다. 그 갯수는 다음과 같다.

| - 리셋 (1개) - 외부 인터럽트 (8개) - 타이머/카운터 관련 인터럽트 (14개) - 각종 통신 관련 인터럽트 (8개) - 그 외 ADC, EEPROM, 아날로그 비교기 (4개) |

위에서부터 우선순위가 가장 높은 순이다.

인터럽트 처리 과정

마이크로 컨트롤러의 인터럽트 처리 과정의 전체적인 맥락은 비슷하지만 세부적인 구조는 종류에 따라 다르다.

| 1. 인터럽트 요청 신호 검출 : 프로그램을 수행하는 도중에 인터럽트 요청이 발생할 경우 해당 장치의 인터럽트 플래그가 세트된다. 이 인터럽트 플래그는 인터럽트 서비스 루틴이 수행되면 자동으로 클리어된다. 2. 인터럽트 요청 허용 여부 판단 : CPU는 해당 장치의 인터럽트 마스크 레지스터의 비트와 SREG의 전역 인터럽트 비트를 보고 허용 여부를 결정한다. 또한, 동시에 발생한 인터럽트 (두개 이상)에 대해서 우선 순위를 결정하게 된다. 3. 인터럽트 벡터 주소로 점프 : AVR은 인터럽트 벡터 주소가 하드웨어적으로 정해져 있어서 그 해당 주소로 점프하게 된다. 4. 복귀 정보 저장 : CPU는 현재의 동작 중인 프로그램의 위치인 프로그램 카운터 (PC) 값을 메모리 스택(Stack)에 저장한다. 또한, 인터럽트 수행 중에 다른 인터럽트의 허용을 막기 위해서 '일시적으로' 인터럽트 금지 상태로 설정한다. 5. 인터럽트 서비스 루틴의 수행 : CPU가 인터럽트 서비스 루틴으로 점프하여 해당 프로그램을 수행한다. 만일, 인터럽트 서비스 루틴 수행 중에 다른 인터럽트를 허용하고자 한다면 여기서 '일시적으로' 금지된 인터럽트 상태를 바꿔 주어야 한다. 6. 주 프로그램으로 복귀 : 인터럽트 수행이 종료되어 RETI 명령어를 만나게 되면 스택에서 프로그램 카운터 값을 찾아와 다시 원래 수행하던 주 프로그램으로 복귀한다. 그리고 전에 '일시적으로' 금지된 인터럽트 상태도 해제된다. |

외부 인터럽트 관련 레지스터

외부 인터럽트와 관련된 레지스터로는 먼저 MCUCR 및 SREG 2개와 퓨즈 비트의 BOOTRET이 있다. MCUCR 및 퓨즈비트 사용은 인터럽트 벡터의 위치를 변경할 때 사용하지만, 보통의 경우에 변경하지 않으므로 MCUCR 및 퓨즈 비트는 잘 사용하지 않는다. 그러나 SREG의 I 비트는 인터럽트를 사용하기 위해 빈번하게 사용하게 된다.

ATmega128은 모두 8개의 외부 인터럽트를 지원한다. 외부 인터럽트와 관련된 레지스터는 EICRA, EICRB, EIMSK, EIFR 총 4개가 있다.

| 1) EICRA : 외부 인터럽트 3, 2, 1, 0의 동작을 설정한다. 2) EICRB : 외부 인터럽트 7, 6, 5, 4의 동작을 설정한다. 3) EIMSK : 외부 인터럽트 7~0의 개별 각각을 허용하기 위해 사용한다. 4) EIFR : 외부 인터럽트의 개별 상태를 나타낸다. |

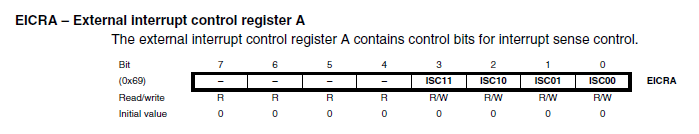

EICRA (External Interrupt Control Resister A)

EICRA 레지스터는 외부 인터럽트 3, 2, 1, 0 동작에 관한 설정을 하는 레지스터이다.

| • BIT 7 - Interrupt Sense Control3 1 - 외부 인터럽트 3의 트리거 방식을 설정 • BIT 6 - Interrupt Sense Control3 0 - 외부 인터럽트 3의 트리거 방식을 설정 • BIT 5 - Interrupt Sense Control2 1 - 외부 인터럽트 2의 트리거 방식을 설정 • BIT 4 - Interrupt Sense Control2 0 - 외부 인터럽트 2의 트리거 방식을 설정 • BIT 3 - Interrupt Sense Control1 1 - 외부 인터럽트 1의 트리거 방식을 설정 • BIT 2 - Interrupt Sense Control1 0 - 외부 인터럽트 1의 트리거 방식을 설정 • BIT 1 - Interrupt Sense Control0 1 - 외부 인터럽트 0의 트리거 방식을 설정 • BIT 0 - Interrupt Sense Control0 0 - 외부 인터럽트 0의 트리거 방식을 설정 |

ISC는 인터럽트를 어떤 시점에서 잡을 것인지를 결정한다. 외부 인터럽트의 변화는 HIGH, LOW의 레벨 변화 및 HIGH ➡ LOW 또는 LOW ➡ HIGH 의 엣지 변화로 입력된다. 이것은 어떤 입력의 변화가 인터럽트를 발생하지를 결정하는 비트이다.

| 번호 | ISCn1 | ISCn0 | 설명 |

| 1 | 0 | 0 | INTn 핀의 LOW 레벨 입력이 인터럽트를 트리거 |

| 2 | 0 | 1 | (reserved) |

| 3 | 1 | 0 | INTn 핀의 Falling Edge가 인터럽트를 비동기적으로 트리거 |

| 4 | 1 | 1 | INTn 핀의 Rising Edge가 인터럽트를 비동기적으로 트리거 |

예를 들어, ISC21 = 1, ISC20 = 0으로 설정하면 '외부 인터럽트 2의 폴링 엣지시에 인터럽트를 발생'이 되어 EICRA = 0x30; 또는 0b00110000; 과 같이 표현된다.

'Embedded System > AVR' 카테고리의 다른 글

| [AVR] 타이머 오버플로우 인터럽트 (0) | 2022.06.10 |

|---|---|

| [AVR] 인터럽트 (Interrupt) (3) (0) | 2022.06.09 |

| [AVR] 인터럽트 (Interrupt) (1) (0) | 2022.06.09 |

| [AVR] CTC 비교매치 모드 인터럽트 (0) | 2022.06.09 |

| [AVR] JMOD-128-1 (0) | 2022.06.09 |